## F2708 1024 x 8 UV Erasable PROM

MOS Memory Products

#### Description

The F2708 is an 8,192-bit ultraviolet light Erasable and electrically Programmable Read Only Memory (EPROM) manufactured using the Isoplanar n-channel silicon gate technology. Organized 1024 x 8, the F2708 is ideally suited for non-volatile data storage in applications such as 8-bit microprocessor systems, where reprogrammability, high bit-density, maximum performance and simple interfacing are essential parameters. All inputs and outputs are TTL compatible. The 3-state outputs become high impedance when the F2708 is deselected, allowing a direct interface capability which is useful in many computer bus structures.

The F2708 provides inexpensive, non-volatile storage of data/program code in applications where fast turn-around and experimentation are important requirements.

- 1024 x 8-BITS ORGANIZATION

- FAST ACCESS TIME -350 ns MAX (F2708-1)

- TTL COMPATIBLE INPUTS AND OUTPUTS

- 3-STATE OUTPUTS

- STANDARD POWER SUPPLIES +12 V, +5 V, -5 V

- CHIP SELECT INPUT FOR MEMORY EXPANSION

- **STATIC OPERATION**

- PIN COMPATIBLE TO 8K AND 16K ROMs FOR LOW-COST PRODUCTION

- **III** LOW POWER DURING PROGRAMMING

- CONTENTS ERASABLE WITH ULTRAVIOLET LIGHT

#### Pin Names

| A <sub>0</sub> -A <sub>9</sub> | Address inputs                  |

|--------------------------------|---------------------------------|

| PRGM                           | Program Pulse Input             |

| CS/WE                          | Chip Select/Write Enable        |

| Q <sub>0</sub> -Q <sub>7</sub> | Data Outputs/Programming Inputs |

| VDD                            | +12 V Supply                    |

| VCC                            | +5 V Supply                     |

| Vss                            | Ground                          |

| V <sub>BB</sub>                | -5 V Supply                     |

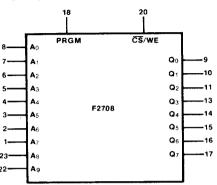

#### Logic Symbol

$V_{DD} = Pin 19$

V<sub>CC</sub> = Pin 24

$V_{BB} = Pin 21$

$V_{SS} = Pin 12$

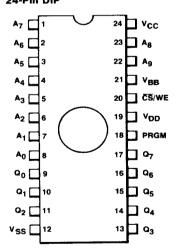

# Connection Diagram 24-Pin DIP

(Top View)

| Package     | Outline | Order Code |

|-------------|---------|------------|

| Ceramic DIP | 7C      | D          |

| Absolute Maximum Ratings                          |                 |

|---------------------------------------------------|-----------------|

| V <sub>DD</sub> Supply Voltage                    | -0.3 V to +20 V |

| V <sub>CC</sub> or V <sub>SS</sub> Supply Voltage | -0.3 V to +15 V |

| PRGM Input Voltage                                |                 |

| During Programming                                | -0.3 V to +35 V |

| CS/WE Input Voltage                               |                 |

| During Programming                                | -0.3 V to +20 V |

| Any Other Input                                   |                 |

| During Programming                                | -0.3 V to +15 V |

| Any Input or Output During Read                   | -0.3 V to +15 V |

| Operating Temperature (Ambient)                   | 0°C to 70°C     |

| Storage Temperature (Ambient)                     | -65°C to +125°C |

| Power Dissipation                                 | 1.8 W           |

All voltages with respect to VBB.

Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

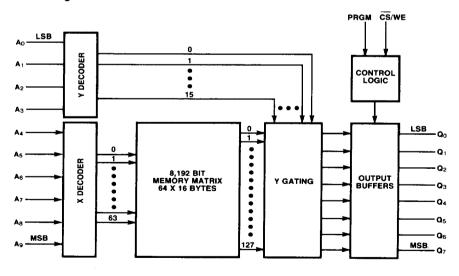

## **Block Diagram**

## F2708

Pin Connections During Read or Programming Modes

| Mode     | Data I/O          | VSS Supply | PRGM        | V <sub>DD</sub> Supply | CS/WE           | V <sub>BB</sub> Supply | V <sub>CC</sub> Supply |

|----------|-------------------|------------|-------------|------------------------|-----------------|------------------------|------------------------|

| моде     | 9-11, 13-17       | 12         | 18          | 19                     | 20              | 21                     | 24                     |

| Read     | Output Data       | GND        | GND         | +12 V                  | VIL             | -5 V                   | +5 V                   |

| Program  | Input Data        | GND        | Pulsed 26 V | +12 V                  | +12 V           | -5 V                   | +5 V                   |

| Deselect | High<br>Impedance | GND        | GND         | +12 V                  | V <sub>IH</sub> | -5 V                   | +5 V                   |

Read Mode dc Electrical Requirements

$T_A = 0$ °C to 70°C unless otherwise indicated. All voltages referenced to VSS

| Symbol                             | Characteristic     | Min   | Тур  | Max                  | Unit | Note |

|------------------------------------|--------------------|-------|------|----------------------|------|------|

| V <sub>DD</sub>                    | Supply Voltage     | 11.4  | 12.0 | 12.6                 | V    |      |

|                                    | Supply Voltage     | 4.75  | 5.0  | 5.25                 | ٧    |      |

| V <sub>CC</sub><br>V <sub>SS</sub> | Supply Voltage     | 0     | 0    | О                    | V    | 1    |

| V <sub>BB</sub>                    | Supply Voltage     | -5.25 | -5.0 | -4.75                | ٧    |      |

| VIH                                | Input HIGH Voltage | 3.0   |      | V <sub>CC</sub> +1.0 | ٧    |      |

| VIL                                | Input LOW Voltage  | Vss   |      | 0.65                 | ٧    |      |

## Read Mode dc Electrical Characteristics

Over full range of voltage and temperature unless otherwise indicated

| Symbol          | Characteristic (1)                               | Min | Тур | Max  | Unit | Note |

|-----------------|--------------------------------------------------|-----|-----|------|------|------|

| I <sub>DD</sub> | Average V <sub>DD</sub> Current                  |     | 50  | 65   | mA   | 2    |

| lcc             | Average V <sub>CC</sub> Current                  |     | 7.5 | 10   | mA   | 2    |

| Івв             | Average V <sub>BB</sub> Current                  |     | 30  | 45   | mA   | 2    |

| lin             | Input Leakage Current                            |     | 1.0 | 10   | μΑ   | 3    |

| lout            | Output Leakage Current                           |     | 1.0 | 10   | μΑ   | 4    |

| VOH             | Output HIGH Voltage                              | 2.4 |     |      | V    |      |

|                 | Output HIGH Voltage<br>I <sub>OH</sub> = -100 μA | 3.7 |     |      | ٧    |      |

| VOL             | Output LOW Voltage                               |     |     | 0.45 | ٧    |      |

| PD              | Power Dissipation TA = 70°C                      |     |     | 800  | mW   | 5    |

| CIN             | Input Capacitance                                |     | 4.0 | 6.0  | pF   | 6    |

| Cour            | Output Capacitance                               |     | 8.0 | 12   | pF   | 7    |

Notes on following page.

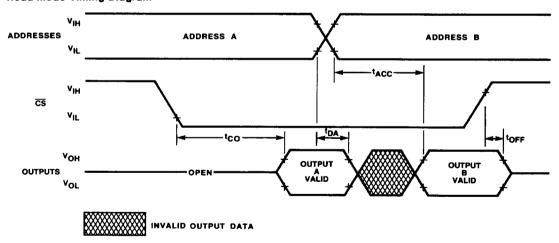

#### Read Mode ac Electrical Characteristics

| Symbol | F                                      |     | F2708-1 |     | F2708 |      |      |

|--------|----------------------------------------|-----|---------|-----|-------|------|------|

|        | Characteristic (Note 8)                | Min | Max     | Min | Max   | Unit | Note |

| tACC   | Address to Output Delay Time           |     | 350     |     | 450   | ns   |      |

| tco    | Chip Select to Output Delay Time       |     | 120     |     | 120   | ns   |      |

| toff   | Chip Deselect to Output High Impedance |     | 120     |     | 120   | ns   |      |

| tDA    | Data Valid After Address Time          | 0   |         | 0   |       | ns   |      |

#### Notes

- 1. All voltage levels are referenced to  $V_{SS} = 0 \text{ V}$ .

- 2. Supply current limits are measured with all inputs HIGH (including CS/WE = 5.0 V) and ambient temperature at  $T_A = 0$ °C.

- 3. Measured both with V<sub>IN</sub> = 5.25 V and V<sub>IN</sub> = V<sub>IL</sub>(min) = V<sub>SS</sub>. 4. Measured both with V<sub>OUT</sub> = 5.5 V and  $\overline{\text{CS}}/\text{WE}$  = 5.0 V.

- 5. The total power dissipation of the 2708 is specified at 800 mW. It is not calculable by summing the various currents (IDD, ICC and IBB) multiplied by their respective voltages, since current paths exist between the various power supplies and VSS. The IDD, ICC and IBB currents should be used to determine power supply capacity only.

- 6. Measured with V<sub>IN</sub> = 0 V,  $T_A$  = 25°C and f = 1.0 MHz. 7. Measured with V<sub>OUT</sub> = 0 V,  $T_A$  = 25°C and f = 1.0 MHz.

- 8. Timing parameters are measured with input logic levels of  $V_{IL(max)} = 0.65 \text{ V}$  and  $V_{IH(min)} = 3.0 \text{ V}$ . Timing measurement reference levels are 0.8 V and 2.8 V for inputs and 0.8 V and 2.4 V for outputs. An output load of 1 TTL gate plus 100 pF is assumed.

#### **Read Mode Timing Diagram**

## F2708

#### **Programming Instructions**

After the completion of an erase operation, every memory cell in the F2708 is in the logic "1" state (as indicated by a HIGH level at the data outputs). An 8-bit byte of data is entered into the memory by programming logic "0s" into the appropriate cell locations at some given address. Word locations in the memory are addressed in the same way as in read operations. Once a cell is programmed to a logic "0", it can be altered only through ultraviolet light erasure.

In order to program the F2708, the  $\overline{\text{CS}}/\text{WE}$  input must first be set to 12 V. Data to be programmed is entered in 8-bit bytes through the output data terminals (Q<sub>0</sub> through Q<sub>7</sub>). Input logic levels for the data lines, addresses, and supply voltages are the same as in a read operation.

Programming is accomplished by executing a number (n) of passes through a programming loop, each of which involves sequencing through all 1024 locations in the address space. In each pass through the loop, a single, high-voltage (26 V) pulse is applied to the PRGM input, once at each address. Logic "Os" applied to the Data outputs (Q0 through Q7) are written into the proper bit positions at the location specified by the Address inputs (A<sub>0</sub> through A<sub>7</sub>). There must be n successive passes through the programming loop in order to guarantee reliable programming of information. The required number of passes through the programming loop (n) is a function of the pulse width (tpw) of the high-voltage programming pulse applied to the PRGM input. Total programming time is given by the relationship:

$$t_{TOTAL} = n \times t_{PW} \ge 100 \text{ ms}$$

(1)

The allowed range of pulse widths is from 0.1 ms to 1.0 ms. This implies that the minimum value of n must be in the range of 100 to 1000. WARNING: Applying more than one programming pulse in succession to the same address is not permitted since it will result in damage to the device. At the end of a program sequence, the  $\overline{CS}/WE$  falling edge transition must occur before the first address transition when changing from the program mode to the read mode. The PRGM pin should be pulled down to approximately

V<sub>SS</sub>, (i.e., ground) with a low impedance device since this pin sources several milliamps of current when  $\overline{\text{CS}}/\text{WE}$  is at 12 V and the PRGM pin is LOW.

#### **Programming Examples**

The programming relationship in Equation 1 above should always be used in determining values of tpw and n.

#### Example 1

The full capacity of 1024 bytes could be programmed using 0.2 ms programming pulse widths. In this case, the minimum number of passes through the programming loop would be

$$n = {t_{TOTAL} \over t_{PW}} = {100 \text{ ms} \over 0.2 \text{ ms}} = 500 \text{ passes}$$

(2)

Each of the 500 passes through the programming loop must sequence through address locations 0 through 1023.

#### Example 2

Word locations 0 to 200 and 300 to 700 are to be programmed. All other bits are "don't care". The programmed pulses are 0.5 ms wide. Thus, the minimum number of passes through the program loop is

$$n = \frac{100 \text{ ms}}{0.5 \text{ ms}} = 200 \text{ passes}$$

(3)

The data entered into the "don't care" locations should consist of all logic "1s". Even though portions of the address space are not used (or "don't care"), the programming loop should still sequence through all 1024 addresses on each pass.

#### Example 3

Extending the case of Example 2, the F2708 is now to be updated to include new data at locations 850 to 880 which previously were programmed as "don't care"; in this case, logic "1s". The mimimum number of passes through the programming loop is the same as in Example 2, n = 200 passes. Address locations 0 to 200 and 300 to 700 must be reprogrammed with their original data pattern. The remaining unused addresses should again be programmed as logic "1s".

#### **Erasing Instructions**

The contents of the F2708 EPROM can be erased by exposure to high-intensity short-wave ultraviolet (UV) light with a wavelength of 2537 Angstroms (Å). This can be accomplished with ultraviolet light EPROM erasure devices which are available from several U.S. manufacturers. These erasure devices contain a UV light source which is usually placed approximately one or two inches from the EPROM to illuminate the transparent window on top of the device. The minimum

required integrated dose (intensity x exposure time) of UV light energy incident on the window of the device in order to reliably insure complete erasure is 12.5 W-s/cm². The UV erasure unit should be periodically calibrated if minimum exposure times are to be used. (Minimum exposure times range from 10 to 45 minutes, depending on model type and age of UV lamp). If longer exposure times are possible, variations in the output light intensity of the UV light source are not critical.

#### Program Mode dc Electrical Requirements T<sub>A</sub> = 25°C ± 5°C unless otherwise indicated

| Symbol              | Characteristic                        |                  | Min   | Тур  | Max                   | Unit          | Note |

|---------------------|---------------------------------------|------------------|-------|------|-----------------------|---------------|------|

| $V_{DD}$            | Supply Voltage                        | Supply Voltage   |       | 12.0 | 12.6                  | v             |      |

| V <sub>CC</sub>     | Supply Voltage                        |                  | 4.75  | 5.0  | 5.25                  | V             |      |

| V <sub>SS</sub>     | Supply Voltage                        |                  | 0     | 0    | 0                     | v             | 1    |

| V <sub>BB</sub>     | Supply Voltage                        |                  | -5.25 | -5.0 | -4.75                 | v             |      |

|                     |                                       | Address and Data | 3.0   |      | V <sub>CC</sub> + 1.0 | v             |      |

| VIHP                | Input HIGH Voltage During Programming | CS/WE Input      | 11.4  | 12.0 | 12.6                  | V             |      |

|                     | During Frogramming                    | PRGM Input       | 25    |      | 27                    | V             | 2    |

| <br>V <sub>IL</sub> | Input LOW Voltage                     | PRGM Input       | VSS   |      | 1.0                   | V             | 2    |

| ¥ IL                | Input COW Voltage                     | All Other Inputs | Vss   |      | 0.65                  | v v v v v v v |      |

#### Program Mode dc Electrical Characteristics $T_A = 25$ °C $\pm$ 5 °C unless otherwise indicated

| Symbol          | Characteristic                             |      | Min | Тур | Max | Unit | Note |

|-----------------|--------------------------------------------|------|-----|-----|-----|------|------|

| lDD             | Average V <sub>DD</sub> Current            |      |     | 50  | 65  | mA   | 3    |

| lcc             | Average V <sub>CC</sub> Current            |      |     | 6.0 | 10  | mA   | 3    |

| I <sub>BB</sub> | Average V <sub>BB</sub> Current            |      |     | 30  | 45  | mA   | 3    |

| lin             | Input Leakage Currer<br>Addresses and CS/V |      | -10 |     | 10  | μΑ   | 4    |

| IPRGM           | PRGM Input Current                         | HIGH |     |     | 20  | mA   |      |

|                 |                                            | LOW  |     |     | 3.0 | mA   | 5    |

## Notes

- 1. All voltage levels are referenced to  $V_{SS} = 0 \text{ V}$ .

- 2. The voltage differential between VIHP and VIL at the PRGM input pin should be greater than or equal to 25 V.

- Supply current limits are measured with all inputs HIGH

(including CS/WE = 5.0 V) and ambient temperature at

T<sub>A</sub> = 0°C.

- 4. Measured both with  $V_{IN} = 5.25 \text{ V}$  and  $V_{IN} = V_{IL(min)} = V_{SS}$ .

- 5. This is a current sourced by the PRGM pin when it is in the LOW state and when CS/WE = 12 V.

| Program Mode ac Flectrical Regultements and Characteristics | T <sub>A</sub> = 25°C + 5°C unless otherwise indicated |  |

|-------------------------------------------------------------|--------------------------------------------------------|--|

| Symbol          | Characteristic                |      | Min | Max | Unit | Note |

|-----------------|-------------------------------|------|-----|-----|------|------|

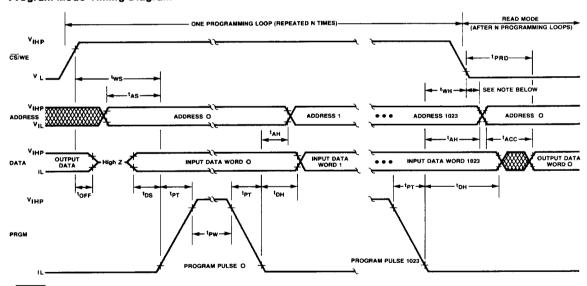

| tas             | Address Set-up Time           |      | 10  |     | μs   |      |

| tah             | Address Hold Time             |      | 1.0 |     | μS   |      |

| tws             | Write Enable Set-up Time      |      | 10  |     | μS   |      |

| twH             | Write Enable Hold Time        |      | 0.5 |     | μS   |      |

| t <sub>DS</sub> | Data Set-up Time              |      | 10  |     | μS   |      |

| tDH             | Data Hold Time                |      | 1.0 |     | μS   |      |

| tpw             | Program Pulse Width           |      | 0.1 | 1.0 | ms   |      |

|                 | Branco Dulas Transition Time  | Rise | 0.5 | 2.0 | μS   |      |

| tpT             | Program Pulse Transition Time | Fall | 0.5 | 2.0 | μS   |      |

| tPRD            | Program to Read Delay         |      |     | 10  | μs   |      |

| toff            | Output Buffer Turn-off Delay  |      | 0   | 120 | ns   |      |

#### **Program Mode Timing Diagram**

## Note

The falling edge of  $\overline{\text{CS}}/\text{WE}$  must occur after the falling edge of the program pulse and before the address transition.

DON'T CARE CONDITION OR INVALID OUTPUT DATA