# 🗖 0257526 0037290 7**29 📰**

# IND: -14/18/24

# MACH215-12/15/20

High-Density EE CMOS Programmable Logic

# DISTINCTIVE CHARACTERISTICS

- 44 Pins

- **32 Output Macrocells**

- **32 Input Macrocells**

- Product terms for:

- Individual flip-flop clock

- Individual asynchronous reset, preset

- Individual output enable

- 12 ns tpp Commercial 14.5 ns tpp Industrial

- 67 MHz fcnt

# **GENERAL DESCRIPTION**

The MACH215 is a member of AMD's high-performance EE CMOS MACH device family. This device has approximately three times the capability of the popular PAL20RA10 without loss of speed. This device is designed for use in asynchronous as well as synchronous applications.

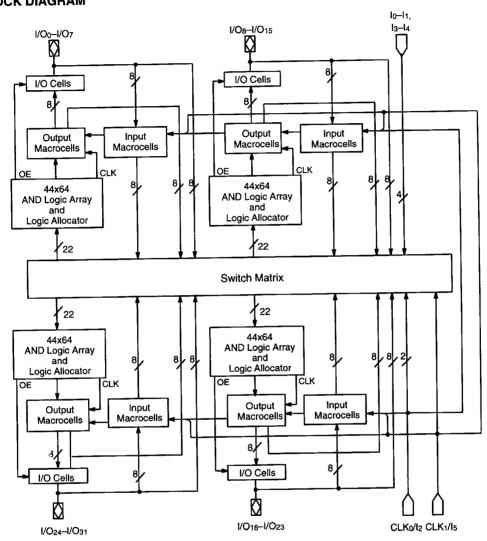

The MACH215 consists of four PAL blocks interconnected by a programmable switch matrix. The four PAL blocks are essentially "PAL22RA8" structures complete with product-term arrays and programmable macrocells, individual register control product terms, and input registers. The switch matrix connects the PAL blocks to each other and to all input pins, providing a high degree of connectivity between the fully-connected PAL blocks. This allows designs to be placed and routed efficiently.

The MACH215 has two kinds of macrocell: output and input. The MACH215 output macrocell provides registered, latched, or combinatorial outputs with programmable polarity. If a registered configuration is chosen, the register can be configured as D-type or T-type to help reduce the number of product terms. The register type decision can be made by the designer or by the software. Each macrocell has its own dedicated clock, asynchronous reset, and asynchronous preset control. The polarity of the clock signal is programmable. All output macrocells can be connected to an I/O cell.

The MACH215 has dedicated input macrocells which provide input registers or latches for synchronizing input signals and reducing setup time requirements.

Advanced Micro Devices

1-161

- 38 Inputs with pull-up resistors

- 32 Outputs

- 64 Flip-flops

- For asynchronous and synchronous applications

- 4 "PAL22RA8" blocks with buried macrocells

- Pin-compatible with MACH110, MACH111, MACH210, and MACH211

FINAL

COM'L: -12/15/20

#

16751E-1

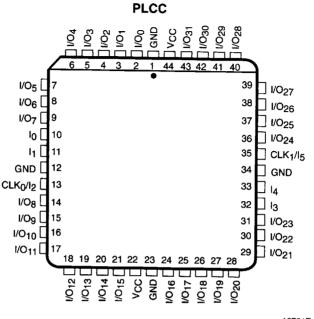

### CONNECTION DIAGRAM Top View

16751E-2

### **PIN DESIGNATIONS**

- CLK/I = Clock or Input

- GND = Ground

- I = Input

- I/O = Input/Output

- Vcc = Supply Voltage

# 02575260037292 5T1 🎟

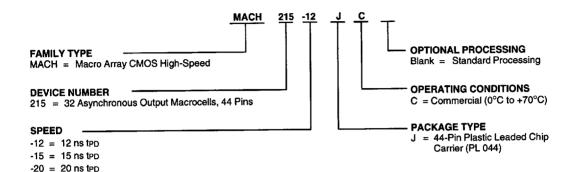

### **ORDERING INFORMATION**

### **Commercial Products**

AMD programmable logic products for commercial applications are available with several ordering options. The order number (Valid Combination) is formed by a combination of:

| Valid Combina | tions |

|---------------|-------|

| MACH215-12    |       |

| MACH215-15    | JC    |

| MACH215-20    |       |

#### Valid Combinations

The Valid Combinations table lists configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations and to check on newly released combinations.

# 0257526 0037293 438 🔳

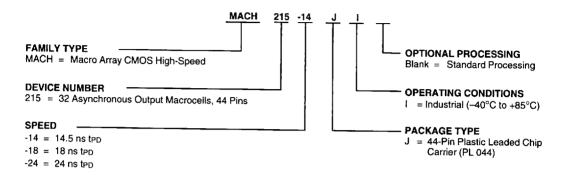

# ORDERING INFORMATION Industrial Products

AMD programmable logic products for industrial applications are available with several ordering options. The order number (Valid Combination) is formed by a combination of:

| Valid Combina | itions |

|---------------|--------|

| MACH215-14    |        |

| MACH215-18    | JI     |

| MACH215-24    | 1      |

#### Valid Combinations

The Valid Combinations table lists configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations and to check on newly released combinations.

# 0257526 0037294 374 📖

### FUNCTIONAL DESCRIPTION

The MACH215 consists of four asynchronous PAL blocks connected by a switch matrix. There are 32 I/O pins and 4 dedicated input pins feeding the switch matrix. These signals are distributed to the four PAL blocks for efficient design implementation. There are also two additional global clock pins that can be used as dedicated inputs. This device provides two kinds of macrocell: output macrocells and input macrocells. This adds greater logic density without affecting the number of pins.

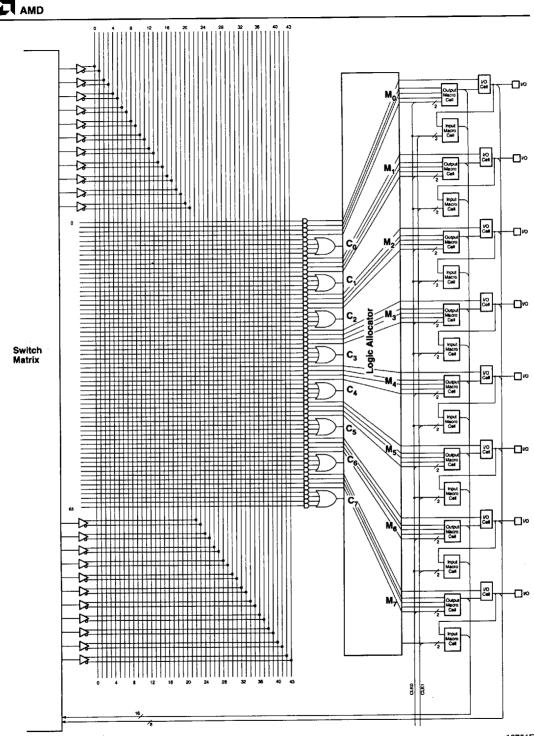

### The PAL Blocks

Each PAL block in the MACH215 (Figure 1) contains a 64-product-term array, a logic allocator, 8 output macrocells, 8 input macrocells, and 8 I/O cells. The switch matrix feeds each PAL block with 22 inputs. This makes the PAL block look effectively like an independent "PAL22RA8" with 8 input macrocells. All flip-flops within the device can operate independently.

### **The Switch Matrix**

The MACH215 switch matrix is fed by the inputs and feedback signals from the PAL blocks. Each PAL block provides 16 internal feedback signals and 8 I/O feedback signals. The switch matrix distributes these signals back to the PAL blocks in an efficient manner that also provides for high performance. The design software automatically configures the switch matrix when fitting a design into the device.

### The Product-term Array

The MACH215 product-term array consists of 32 product terms for logic use and 32 product terms for generating macrocell control signals.

### **The Logic Allocator**

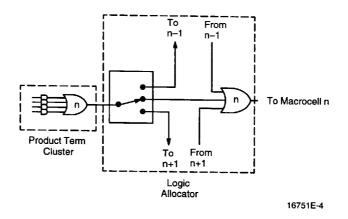

The logic allocator in the MACH215 (Figure 2) takes the 32 logic product terms and allocates them to the 16 macrocells as needed. Each macrocell can be driven by up to 12 product terms. The design software automatically configures the logic allocator when fitting the design into the device.

Table 1 illustrates which product term clusters are available to each macrocell within a PAL block. Refer to Figure 1 for cluster and macrocell numbers.

#### **Table 1. Logic Allocation**

| Output Macrocell | Available<br>Clusters |

|------------------|-----------------------|

| Mo               | Co, C1                |

| M1               | C0, C1, C2            |

| M2               | C1, C2, C3            |

| Мз               | C2, C3, C4            |

| M4               | C3, C4, C5            |

| M5               | C4, C5, C6            |

| M6               | C5, C6, C7            |

| M7               | C6, C7                |

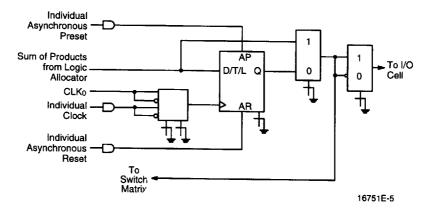

### The Macrocell

There are two types of macrocell in the MACH215: output macrocells and input macrocells. The output macrocell takes the logic of the device and provides it to I/O pins and/or provides feedback for additional logic generation. The input macrocell allows I/O pins to be configured as registered or latched inputs.

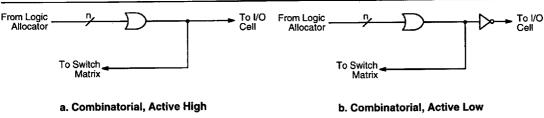

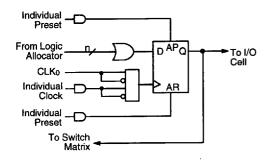

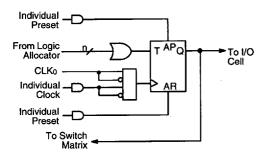

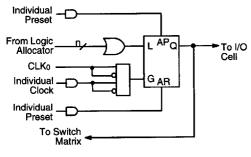

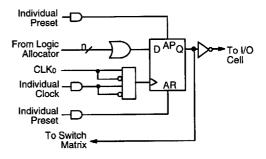

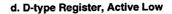

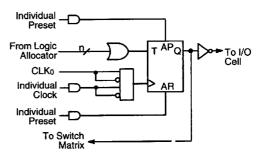

The output macrocell (Figure 3) can generate registered or combinatorial outputs. In addition, a transparent-low latched configuration is provided. If used, the register can be configured as a T-type or a D-type flip-flop. Register and latch functionality is defined in Table 2. Programmable polarity and the T-type flip-flop both give the software a way to minimize the number of product terms needed. These choices can be made automatically by the software when it fits the design into the device.

| Configuration | D/T         | CLK/LE*                       | Q+    |

|---------------|-------------|-------------------------------|-------|

| D-Register    | X           | 0, 1, ↓ (↑)                   | Q     |

|               | 0           | ↑ (↓)                         | 0     |

|               | 1           | ↑ (↓)                         | 1     |

| T-Register    | X<br>0<br>1 | 0, 1, ↓ (↑)<br>↑ (↓)<br>↑ (↓) | a ala |

| Latch         | X           | 1 (0)                         | Q     |

|               | 0           | 0 (1)                         | 0     |

|               | 1           | 0 (1)                         | 1     |

Table 2. Register/Latch Operation

\*Polarity of CLK/LE can be programmed.

# 0257526 0037295 200 🔳

The output macrocell sends its output back to the switch matrix, via internal feedback, and to the I/O cell. The feedback is always available regardless of the configuration of the I/O cell. This allows for buried combinatorial or registered functions, freeing up the I/O pins for use as inputs if not needed as outputs. The basic output macrocell configurations are shown in Figure 4.

The clock/latch-enable for each individual output macrocell can be driven by one of four signals. Two of the signals are provided by the global clock pin  $CLK_0/LE_0$ ; either polarity may be chosen. The other two signals come from a product term provided for each output macrocell. Either polarity of the logic generated by the product term can be chosen. The global clock pin is also available as an input, although care must be taken when a signal acts as both clock and input to the same device.

Each individual output macrocell also has a product term for asynchronous reset and a product term for asynchronous preset. This means that any register or latch may be reset or preset without affecting any other register or latch in the device. The functionality of the flip-flops with respect to initialization is illustrated in Table 3.

Table 3. Asynchronous Reset/Preset Operation

| AR | AP | CLK/LE | Q+           |

|----|----|--------|--------------|

| 0  | 0  | X      | See Table 12 |

| 0  | 1  | Х      | 1            |

| 1  | 0  | X      | 0            |

| 1  | 1  | X      | 0            |

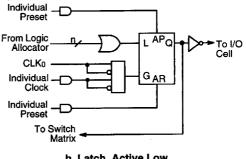

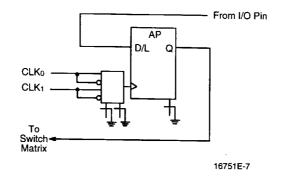

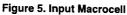

The input macrocell (Figure 5) consists of a flip-flop that can be used to provide registered or latched inputs. The flip-flop can be clocked by either polarity of one of the two global clock/latch-enable pins.

Reset or preset are not provided for these flip-flops. If combinatorial inputs are desired, this macrocell is not used, and the feedback from the I/O pin is used directly. Both the I/O pin feedback and the output of the input register or latch are always available to the switch matrix.

Possible input macrocell configurations are shown in Figure 6.

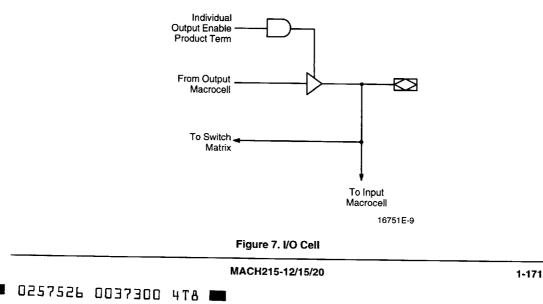

### The I/O Cell

The I/O cell (Figure 7) provides a three-state output buffer. The three-state control is provided by an individual product term for each I/O cell. Depending on the logic programmed onto this product term, the I/O pin can be configured as an output, an input, or a bidirectional pin. The feedback from the I/O pin is always available to the switch matrix, regardless of the state of the output buffer or the output macrocell.

# 02575260037296147 🔳

16751E-3

Figure 1. MACH215 PAL Block MACH215-12/15/20

■ 0257526 0037297 083 ■

Figure 2. Product Term Clusters and the Logic Allocator

c. D-type Register, Active High

e. T-type Register, Active High

g. Latch, Active High

f. T-type Register, Active Low

h. Latch, Active Low

16751E-6

MACH215-12/15/20

0257526 0037299 956

#

## **ABSOLUTE MAXIMUM RATINGS**

| Storage Temperature                                                |

|--------------------------------------------------------------------|

| Ambient Temperature<br>with Power Applied                          |

| Supply Voltage with                                                |

| Respect to Ground0.5 V to +7.0 V                                   |

| DC Input Voltage0.5 V to Vcc + 0.5 V                               |

| DC Output or I/O                                                   |

| Pin Voltage                                                        |

| Static Discharge Voltage 2001 V                                    |

| Latchup Current                                                    |

| $(T_A = 0^{\circ}C \text{ to } +70^{\circ}C) \dots 200 \text{ mA}$ |

| Stresses above those listed under Absolute Maximum Ratings         |

Stresses above those listed under Absolute Maximum Ratings may cause permanent device failure. Functionality at or above these limits is not implied. Exposure to Absolute Maximum Ratings for extended periods may affect device reliability. Programming conditions may differ.

### **OPERATING RANGES** Commercial (C) Devices

Temperature (T<sub>A</sub>) Operating in Free Air . . . . . . . . . . . . . . . . 0°C to +70°C

| Supply Voltage (Vcc) with |                    |

|---------------------------|--------------------|

| Respect to Ground         | +4.75 V to +5.25 V |

Operating ranges define those limits between which the functionality of the device is guaranteed.

# DC CHARACTERISTICS over COMMERCIAL operating ranges unless otherwise specified

| Parameter<br>Symbol | Parameter Description                    | Test Conditions                                                                                                   | Min | Тур | Мах  | Unit |

|---------------------|------------------------------------------|-------------------------------------------------------------------------------------------------------------------|-----|-----|------|------|

| Vон                 | Output HIGH Voltage                      | $I_{OH} = -3.2 \text{ mA}, V_{CC} = Min$<br>$V_{IN} = V_{IH} \text{ or } V_{IL}$                                  | 2.4 |     |      | v    |

| Vol                 | Output LOW Voltage                       | l <sub>OL</sub> = 24 mA, V <sub>CC</sub> = Min<br>V <sub>IN</sub> = V <sub>IH</sub> or V <sub>IL</sub> (Note 1)   |     |     | 0.5  | v    |

| Vін                 | Input HIGH Voltage                       | Guaranteed Input Logical HIGH<br>Voltage for all Inputs (Note 2)                                                  | 2.0 |     |      | >    |

| VIL                 | Input LOW Voltage                        | Guaranteed Input Logical LOW<br>Voltage for all Inputs (Note 2)                                                   |     |     | 0.8  | V    |

| lıн                 | Input HIGH Current                       | V <sub>IN</sub> = 5.25 V, V <sub>CC</sub> = Max (Note 3)                                                          |     |     | 10   | μA   |

|                     | Input LOW Current                        | V <sub>IN</sub> = 0 V, V <sub>CC</sub> = Max (Note 3)                                                             |     |     | -100 | μA   |

| lozн                | Off-State Output Leakage<br>Current HIGH | V <sub>OUT</sub> = 5.25 V, V <sub>CC</sub> = Max<br>V <sub>IN</sub> = V <sub>IH</sub> or V <sub>IL</sub> (Note 3) |     |     | 10   | μA   |

| loz∟                | Off-State Output Leakage<br>Current LOW  | $V_{OUT} = 0 V, V_{CC} = Max$<br>$V_{IN} = V_{IH} \text{ or } V_{IL} \text{ (Note 3)}$                            |     |     | -100 | μA   |

| Isc                 | Output Short-Circuit Current             | V <sub>OUT</sub> = 0.5 V, V <sub>CC</sub> = Max (Note 4)                                                          | -30 |     | -160 | mA   |

| lcc                 | Supply Current (Typical)                 | V <sub>CC</sub> = 5 V, T <sub>A</sub> = 25°C, f = 25 MHz<br>(Note 5)                                              |     | 95  |      | mA   |

#### Notes:

1. Total IoL for one PAL block should not exceed 128 mA.

2. These are absolute values with respect to device ground and all overshoots due to system or tester noise are included. 3. I/O pin leakage is the worst case of IIL and IozL (or IIH and IozH).

Not more than one output should be shorted at a time and duration of the short-circuit should not exceed one second.

Vour = 0.5 V has been chosen to avoid test problems caused by tester ground degradation.

Measured with a 16-bit up/down counter pattern. This pattern is programmed in each PAL block and is capable of being loaded, enabled, and reset.

# CAPACITANCE (Note 1)

| Parameter<br>Symbol | Parameter Description | Test Conditio | Test Conditions                      |   |    |  |

|---------------------|-----------------------|---------------|--------------------------------------|---|----|--|

| CIN                 | Input Capacitance     | VIN = 2.0 V   | $V_{CC} = 5.0 V, T_A = 25^{\circ}C,$ | 6 | ρF |  |

| Соит                | Output Capacitance    | Vout = 2.0 V  | f = 1 MHz                            | 8 | pF |  |

# SWITCHING CHARACTERISTICS over COMMERCIAL operating ranges (Note 2)

| Parameter        | -                                                                                   |                                                       |                                        |          |      | 2    |      | 5    | 1    | 20     |     |

|------------------|-------------------------------------------------------------------------------------|-------------------------------------------------------|----------------------------------------|----------|------|------|------|------|------|--------|-----|

| Symbol           | Parameter Description                                                               |                                                       |                                        | Min      | Max  | Min  | Max  | Min  | Max  | Unit   |     |

| t <sub>PD</sub>  | Input, I/O, or Feedback to Combinatorial Output (Note 3)                            |                                                       |                                        | 3        | 12   | 3    | 15   | 3    | 20   | ns     |     |

| tsa              | Setup Time                                                                          | Time from Input, I/O, or                              |                                        | D-type   | 5    |      | 6    |      | 8    |        | пѕ  |

|                  | Feedback to                                                                         | Product Term Clock                                    |                                        | T-type   | 6    |      | 7    |      | 9    |        | ns  |

| tна              | Register Dat                                                                        | ta Hold Time Using P                                  | roduct Term Cloc                       | k        | 5    |      | 6    |      | 8    | ······ | ns  |

| tcoa             | Product Terr                                                                        | m Clock to Output (No                                 | ote 3)                                 |          | 4    | 14   | 4    | 18   | 4    | 22     | ns  |

| twla             | Product Tor                                                                         | m, Clock Width                                        |                                        | LOW      | 8    |      | 9    |      | 12   |        | ns  |

| twha             | 1 TOGUCE TEN                                                                        |                                                       |                                        | HIGH     | 8    |      | 9    |      | 12   |        | ns  |

|                  | Maximum                                                                             |                                                       |                                        | D-type   | 52.6 |      | 41.7 |      | 33.3 |        | MHz |

|                  | Frequency<br>Using                                                                  | External Feedback                                     | 1/(tsa + tcoa)                         | T-type   | 50   |      | 40   |      | 32.2 |        | MHz |

| fmaxa            | Product                                                                             |                                                       |                                        | D-type   | 58.8 |      | 45.5 |      | 35.7 |        | MHz |

|                  | Term<br>Clock                                                                       | Internal Feedback (i                                  | ÍCNTA)                                 | T-type   | 55.6 |      | 43.5 |      | 34.5 |        | MHz |

|                  | (Note 1)                                                                            | No Feedback                                           | 1/(twla + twha)                        | <u> </u> | 62.5 | _    | 55.6 |      | 41.7 |        | MHz |

| tss              | Setup Time from Input, I/O,<br>or Feedback to Global Clock                          |                                                       |                                        | D-type   | 7    |      | 10   |      | 13   |        | ns  |

| .55              |                                                                                     |                                                       |                                        | T-type   | 8    |      | 11   |      | 14   |        | ns  |

| tHS              | Register Data Hold Time Using Global Clock                                          |                                                       |                                        | 0        |      | 0    | ·    | 0    |      | ns     |     |

| tcos             | Global Clock to Output (Note 3)                                                     |                                                       |                                        | 2        | 8    | 2    | 10   | 2    | 12   | ns     |     |

| twLs             |                                                                                     |                                                       |                                        | LOW      | 6    |      | 6    |      | 8    |        | ns  |

| twнs             | Global Clock Width                                                                  |                                                       |                                        | HIGH     | 6    |      | 6    |      | 8    |        | ns  |

|                  | Maximum                                                                             | Aaximum<br>Frequency External Feedback 1/(tss + tcos) | D-type                                 | 66.7     |      | 50   |      | 40   |      | MHz    |     |

|                  | Frequency<br>Using                                                                  |                                                       | T-type                                 | 62.5     |      | 47.6 |      | 38.5 |      | MHz    |     |

| <b>fmaxs</b>     | Global                                                                              |                                                       | <u> </u>                               | D-type   | 83.3 |      | 66.6 |      | 50   |        | MHz |

|                  | Clock<br>(Note 1)                                                                   | Internal Feedback (                                   | fonts)                                 | T-type   | 76.9 |      | 62.5 |      | 47.6 |        | MHz |

|                  | (NOIE I)                                                                            | No Feedback                                           | 1/(twis + twis)                        | <u> </u> | 83.3 |      | 83.3 |      | 62.5 |        | MHz |

| tsla             | Setup Time f<br>or Feedback                                                         | rom Input, I/O,<br>to Product Term Gat                |                                        |          | 5    |      | 6    |      | 8    |        | ns  |

| thla             |                                                                                     | Iold Time Using Prod                                  |                                        |          | 5    |      | 6    |      | 8    |        | ns  |

| <b>t</b> GOA     | Product Terr                                                                        | n Gate to Output (Not                                 | ie 3)                                  |          |      | 16   |      | 19   |      | 22     |     |

| tgwa             | Product Term Gate Width LOW (for LOW transparent)<br>or HIGH (for HIGH transparent) |                                                       |                                        | 8        |      | 9    |      | 12   |      | ns     |     |

| tsls             | Setup Time from Input, I/O, or Feedback to Global Gate                              |                                                       |                                        | 7        |      | 10   |      | 13   |      | ns     |     |

| t <sub>HLS</sub> |                                                                                     | lold Time Using Glob                                  |                                        |          | 0    |      | 0    |      | 0    |        |     |

| tgos             | Gate to Outp                                                                        |                                                       | ······································ |          |      | 10   |      | 11   |      | 12     | ns  |

| tgws             | Global Gate<br>or HIGH (for                                                         | Width LOW (for LOW HIGH transparent)                  | transparent)                           | <u>-</u> | 6    |      | 6    |      | 8    |        | ns  |

# SWITCHING CHARACTERISTICS over COMMERCIAL operating ranges (Note 2) (continued)

| Parameter     |                                                                                                                 |        | -12  | 2   | -1   | -15 -20 |      | )   |      |

|---------------|-----------------------------------------------------------------------------------------------------------------|--------|------|-----|------|---------|------|-----|------|

| Symbol        | Parameter Description                                                                                           |        | Min  | Max | Min  | Max     | Min  | Max | Unit |

| <b>t</b> PDL  | Input, I/O, or Feedback to Output Through<br>Transparent Input or Output Latch                                  |        |      | 14  |      | 17      |      | 22  | ns   |

| tsia          | Input Register Setup Time                                                                                       |        | 2    |     | 2    |         | 2    |     | ns   |

| tHIR          | Input Register Hold Time                                                                                        |        | 2    |     | 2.5  |         | 3    |     | ns   |

| tico          | Input Register Clock to Combinatorial Output                                                                    |        |      | 15  |      | 18      |      | 23  | ns   |

| tics          | Input Register Clock to Output Register Setup                                                                   | D-type | 12   |     | 15   |         | 20   |     | ns   |

|               |                                                                                                                 | T-type | 13   |     | 16   |         | 21   |     | ns   |

| twici         | Input Register Clock Width                                                                                      | LOW    | 6    |     | 6    |         | 8    |     | ns   |

| twich         |                                                                                                                 | HIGH   | 6    |     | 6    |         | 8    |     | ns   |

| fmaxir        | Maximum Input Register Frequency 1/(twicL +                                                                     | twicн) | 83.3 |     | 83.3 |         | 62.5 |     | MH:  |

| tsiL          | Input Latch Setup Time                                                                                          |        | 2    |     | 2    |         | 2    |     | ns   |

| t⊢ı∟          | Input Latch Hold Time                                                                                           |        | 2    |     | 2.5  |         | 3    |     | ns   |

| tigo          | Input Latch Gate to Combinatorial Output                                                                        |        |      | 17  |      | 20      |      | 25  | ns   |

| tigol         | Input Latch Gate to Output Through Transparent<br>Output Latch                                                  |        | 19   |     | 22   |         | 27   | ns  |      |

| tslla         | Setup Time from Input, I/O, or Feedback Through<br>Transparent Input Latch to Product Term Output<br>Latch Gate |        |      |     | 8    |         | 10   |     | ns   |

| tigsa         | Input Latch Gate to Output Latch Setup Using<br>Product Term Output Latch Gate                                  |        |      |     | 8    |         | 10   |     | ns   |

| tsus          | Setup Time from Input, I/O, or Feedback Through<br>Transparent Input Latch to Global Output Latch Gate          |        |      |     | 12   |         | 15   |     | ns   |

| tiess         | Input Latch Gate to Output Latch Setup Using Global<br>Output Latch Gate                                        |        |      |     | 16   |         | 21   |     | ns   |

| twigL         | Input Latch Gate Width LOW                                                                                      |        | 6    |     | 6    |         | 8    |     | ns   |

| <b>t</b> PDLL | Input, I/O, or Feedback to Output Through Trans<br>Input and Output Latches                                     | parent |      | 16  |      | 19      |      | 24  | ns   |

| tan           | Asynchronous Reset to Registered or Latched O                                                                   | utput  |      | 16  |      | 20      |      | 25  | ns   |

| tanw          | Asynchronous Reset Width (Note 1)                                                                               |        | 12   |     | 15   |         | 20   |     | ns   |

| tarr          | Asynchronous Reset Recovery Time (Note 1)                                                                       |        |      |     | 10   |         | 15   |     | ns   |

| tap           | Asynchronous Preset to Registered or Latched Output                                                             |        |      | 16  |      | 20      |      | 25  | ns   |

| tapw          | Asynchronous Preset Width (Note 1)                                                                              |        | 12   |     | 15   |         | 20   | L   | ns   |

| tapr          | Asynchronous Preset Recovery Time (Note 1)                                                                      |        | 8    |     | 10   |         | 15   |     | ns   |

| tea           | Input, I/O, or Feedback to Output Enable (Note 3                                                                | )      | 2    | 12  | 2    | 15      | 2    | 20  | ns   |

| ter           | Input, I/O, or Feedback to Output Disable (Note                                                                 | 3)     | 2    | 12  | 2    | 15      | 2    | 20  | ns   |

Notes:

These parameters are not 100% tested, but are evaluated at initial characterization and at any time the design is modified where frequency may be affected.

See Switching Test Circuit for test conditions. Switching waveforms illustrate true clocks only. Switching waveforms can be used to illustrate both synchronous and asynchronous clock timing. For example, tss is the ts parameter for synchronous clocks and tsh is the ts parameter for asynchronous clocks.

3. Parameters measured with 16 outputs switching.

MACH215-12/15/20 (Com'l)

🖩 0257526 0037303 107 🛲

### ABSOLUTE MAXIMUM RATINGS

| Storage Temperature65°C to +150°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ambient Temperature<br>with Power Applied55°C to +125°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Supply Voltage with<br>Respect to Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| DC Input Voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| DC Output or                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| I/O Pin Voltage0.5 V to Vcc + 0.5 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Static Discharge Voltage 2001 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Latchup Current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| $(T_A = -40^{\circ}C \text{ to } +85^{\circ}C) \dots 200 \text{ mA}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Streepenshows the set of the set |

Stresses above those listed under Absolute Maximum Ratings may cause permanent device failure. Functionality at or above these limits is not implied. Exposure to Absolute Maximum Ratings for extended periods may affect device reliability. Programming conditions may differ.

# INDUSTRIAL OPERATING RANGES

| Ambient Temperature (T <sub>A</sub> )<br>Operating in Free Air40°C to +85°C |

|-----------------------------------------------------------------------------|

| Supply Voltage (V <sub>CC</sub> ) with<br>Respect to Ground                 |

Operating ranges define those limits between which the functionality of the device is guaranteed.

# DC CHARACTERISTICS over INDUSTRIAL operating ranges unless otherwise specified

| Parameter<br>Symbol | Parameter Description                    | Test Conditions                                                                                                 | Min<br>2.4 | Тур | Max  | Unit |  |

|---------------------|------------------------------------------|-----------------------------------------------------------------------------------------------------------------|------------|-----|------|------|--|

| Voн                 | Output HIGH Voltage                      | $l_{OH} = -3.2 \text{ mA}, V_{CC} = Min$<br>$V_{IN} = V_{IH} \text{ or } V_{IL}$                                |            |     |      | V    |  |

| Vol                 | Output LOW Voltage                       | I <sub>OL</sub> = 24 mA, V <sub>CC</sub> = Min<br>V <sub>IN</sub> = V <sub>IH</sub> or V <sub>IL</sub> (Note 1) |            |     | 0.5  | v    |  |

| ViH                 | Input HIGH Voltage                       | Guaranteed Input Logical HIGH<br>Voltage for all Inputs (Note 2)                                                | 2.0        |     |      | V    |  |

| VIL                 |                                          |                                                                                                                 |            |     | 0.8  | v    |  |

| lin                 | Input HIGH Leakage Current               | V <sub>IN</sub> = 5.25 V, V <sub>CC</sub> = Max (Note 3)                                                        |            |     | 10   | μA   |  |

| l <sub>iL</sub>     | Input LOW Leakage Current                | VIN = 0 V, Vcc = Max (Note 3)                                                                                   |            |     | -100 | μA   |  |

| lozh                | Off-State Output Leakage<br>Current HIGH | $V_{OUT} = 5.25 \text{ V}, V_{CC} = \text{Max}$<br>$V_{IN} = V_{IH} \text{ or } V_{IL} \text{ (Note 3)}$        |            |     | 10   | μA   |  |

| lozi                | Off-State Output Leakage<br>Current LOW  | $V_{OUT} = 0 V, V_{CC} = Max$<br>$V_{IN} = V_{IH} \text{ or } V_{IL} (Note 2)$                                  |            |     | -100 | μA   |  |

| Isc                 | Output Short-Circuit Current             | Vout = 0.5 V, Vcc = Max (Note 4)                                                                                | -30        |     | -160 | mA   |  |

| lcc                 | Supply Current (Typical)                 | Vcc = 5 V, T <sub>A</sub> = 25°C, f = 25 MHz (Note 5)                                                           |            | 95  |      | mA   |  |

Notes:

1. Total IoL for one PAL block should not exceed 128 mA.

**0**257526 0037304 043 **1**

2. These are absolute values with respect to device ground and all overshoots due to system and/or tester noise are included.

3. I/O pin leakage is the worst case of IIL and IozL (or IIH and IozH).

4. Not more than one output should be shorted at a time. Duration of the short-circuit should not exceed one second. Vour = 0.5 V has been chosen to avoid test problems caused by tester ground degradation.

Measured with a 16-bit up/down counter pattern. This pattern is programmed in each PAL block and is capable of being loaded, enabled, and reset.

# CAPACITANCE (Note 1)

| Parameter<br>Symbol | Parameter Description | Test Conditio           | ons                                                                  | Тур | Unit |

|---------------------|-----------------------|-------------------------|----------------------------------------------------------------------|-----|------|

| Cin                 | Input Capacitance     | V <sub>IN</sub> = 2.0 V | $V_{CC} = 5.0 \text{ V}, \text{ T}_{\text{A}} = 25^{\circ}\text{C},$ | 6   | pF   |

| Cour                | Output Capacitance    | Vout = 2.0 V            | f = 1 MHz                                                            | 8   | pF   |

# SWITCHING CHARACTERISTICS over INDUSTRIAL operating ranges (Note 2)

| Parameter        |                                                                                     |                                         | -14                    | ŧ      | -18  |      | -24  |      |      |      |     |

|------------------|-------------------------------------------------------------------------------------|-----------------------------------------|------------------------|--------|------|------|------|------|------|------|-----|

| Symbol           |                                                                                     |                                         | Min                    | Max    | Min  | Max  | Min  | Max  | Unit |      |     |

| teo              | Input, I/O, or Feedback to Combinatorial Output<br>(Note 3)                         |                                         |                        |        | 14.5 |      | 18   |      | 24   | ns   |     |

| tsa              | Setup Time f                                                                        | from Input, I/O, or                     |                        | D-type | 6    |      | 7.5  |      | 10   |      | ns  |

| LSA              | Feedback to                                                                         | Product Term Clock                      |                        | T-type | 7.5  |      | 8.5  |      | 11   |      | ns  |

| tна              | Register Dat                                                                        | a Hold Time Using P                     | roduct Term Cloc       | k      | 6    |      | 7.5  |      | 10   |      | ns  |

| tcoa             | Product Term                                                                        | n Clock to Output (No                   | ote 3)                 |        |      | 17   |      | 22   |      | 26.5 | ns  |

| twla             | Product Terr                                                                        | n, Clock Width                          |                        | LOW    | 10   |      | 11   |      | 15   |      | ns  |

| twha             | 1 Youddt Foll                                                                       |                                         |                        | HIGH   | 10   |      | 11   |      | 15   |      | ns  |

|                  | Maximum                                                                             | External Feedback                       | $1/(t_{SA} + t_{COA})$ | D-type | 42   |      | 33   |      | 26.5 |      | MHz |

|                  | Frequency<br>Using                                                                  | EXIGINAL FEEDDACK                       | IT(ISA + ICOA)         | T-type | 40   |      | 32   |      | 25.5 |      | MHz |

| fmaxs            | Product                                                                             |                                         |                        | D-type | 47   |      | 36   |      | 28.5 |      | MHz |

| IMAXS            | Term                                                                                | Internal Feedback (fcnta)               |                        | T-type | 44   |      | 34.5 |      | 27.5 |      | MHz |

|                  | Clock<br>(Note 1)                                                                   | No Feedback                             | 1/(twla + twha)        |        | 50   |      | 44.5 |      | 33   |      | MHz |

|                  | Setup Time f                                                                        | Time from Input, I/O,                   |                        | D-type | 8.5  |      | 12   |      | 16   |      | ns  |

| tss              | or Feedback to Global Clock T-type                                                  |                                         |                        | 10     |      | 13.5 |      | 17   |      | ns   |     |

| t <sub>HS</sub>  | Register Dat                                                                        | a Hold Time Using G                     | lobal Clock            |        | 0    |      | 0    |      | 0    |      | ns  |

| tcos             | Giobal Clock                                                                        | to Output (Note 3)                      |                        |        |      | 10   |      | 12   |      | 14.5 | ns  |

| twis             |                                                                                     |                                         |                        | LOW    | 7.5  |      | 7.5  |      | 10   |      | ns  |

| twhs             | Global Clock                                                                        | Width                                   |                        | HIGH   | 7.5  |      | 7.5  |      | 10   |      | ns  |

|                  | Maximum                                                                             | External Feedback                       | 1/(tss + 100s)         | D-type | 53   |      | 40   |      | 32   |      | MHz |

|                  | Frequency<br>Using<br>Global<br>Clock                                               |                                         |                        | T-type | 50   |      | 38   |      | 30.5 |      | MHz |

| <b>f</b> MAXS    |                                                                                     | Internal Feedback (                     | (fonts)                | D-type | 66.5 |      | 53   |      | 40   |      | MHz |

|                  |                                                                                     |                                         |                        | T-type | 61.5 |      | 50   |      | 38   |      | MHz |

|                  | (Note 1) No Feedback 1/(twis + twis)                                                |                                         |                        | 66.5   |      | 66.5 |      | 50   |      | MHz  |     |

| tsla             |                                                                                     | from Input, I/O,<br>to Product Term Gat | e                      |        | 6    |      | 7.5  |      | 10   |      | ns  |

| <b>t</b> hla     |                                                                                     | Iold Time Using Proc                    |                        |        | 6    |      | 7.5  |      | 10   |      | ns  |

| tgoa             | Product Terr                                                                        | m Gate to Output (No                    | te 3)                  |        |      | 19.5 |      | 23   |      | 26.5 | ns  |

| tgwa             | Product Term Gate Width LOW (for LOW transparent)<br>or HIGH (for HIGH transparent) |                                         | 10                     |        | 11   |      | 14.5 |      | ns   |      |     |

| tsLs             | Setup Time from Input, I/O, or Feedback to Global Gate                              |                                         |                        | 8.5    |      | 12   | i    | 16   |      | ns   |     |

| t <sub>HLS</sub> | Latch Data Hold Time Using Global Gate                                              |                                         | 0                      |        | 0    |      | 0    |      | ns   |      |     |

| tgos             | Gate to Outp                                                                        |                                         |                        |        |      | 12   |      | 13.5 |      | 14.5 | ns  |

| taws             | Global Gate<br>or HIGH (for                                                         | Width LOW (for LOW HIGH transparent)    | / transparent)         |        | 7.5  |      | 7.5  |      | 10   |      | ns  |

# SWITCHING CHARACTERISTICS over INDUSTRIAL operating ranges (Note 2) (continued)

| Parameter                |                                                                                                                 |        | -1   | -14  |      | -18  |      | -24  |      |

|--------------------------|-----------------------------------------------------------------------------------------------------------------|--------|------|------|------|------|------|------|------|

| Symbol                   | Parameter Description                                                                                           |        | Min  | Max  | Min  | Max  | Min  | Max  | Unit |

| t <sub>PDL</sub>         | Input, I/O, or Feedback to Output Through<br>Transparent Input or Output Latch                                  |        |      | 17   |      | 20.5 |      | 26.5 | ns   |

| tsir                     | Input Register Setup Time                                                                                       |        | 2.4  |      | 2.4  |      | 2.4  |      | ns   |

| t <sub>HIR</sub>         | Input Register Hold Time                                                                                        |        | 3    |      | 3.5  |      | 4    |      | ns   |

| tico                     | Input Register Clock to Combinatorial Output                                                                    |        |      | 18   |      | 22   |      | 28   | ns   |

| tics                     | Input Register Clock to Output Register Setup                                                                   | D-type | 14.5 |      | 18   |      | 24   |      | ns   |

|                          |                                                                                                                 | T-type | 16   |      | 19.5 |      | 25.5 |      | ns   |

| twicL                    |                                                                                                                 | LOW    | 7.5  |      | 7.5  |      | 10   |      | ns   |

| twich                    | Input Register Clock Width                                                                                      | HIGH   | 7.5  |      | 7.5  |      | 10   |      | ns   |

| <b>f<sub>MAXIR</sub></b> | Maximum Input Register Frequency 1/(twicL + tw                                                                  | vicн)  | 66.5 |      | 66.5 |      | 50   |      | MHz  |

| tsil                     | Input Latch Setup Time                                                                                          |        | 2.5  |      | 2.5  |      | 2.5  |      | ns   |

| t <sub>HiL</sub>         | Input Latch Hold Time                                                                                           |        | 3    |      | 3.5  |      | 4    |      | ns   |

| tigo                     | Input Latch Gate to Combinatorial Output                                                                        |        |      | 20.5 |      | 24   |      | 30   | ns   |

| tigol                    | Input Latch Gate to Output Through Transparent<br>Output Latch                                                  |        |      | 23   |      | 26.5 |      | 32.5 | ns   |

| <b>t</b> slla            | Setup Time from Input, I/O, or Feedback Through<br>Transparent Input Latch to Product Term Output<br>Latch Gate |        | 8.5  |      | 10   |      | 12   | ·    | ns   |

| tigsa                    | Input Latch Gate to Output Latch Setup Using<br>Product Term Output Latch Gate                                  |        | 8.5  |      | 10   | -    | 12   |      | ns   |

| tsils                    | Setup Time from Input, I/O, or Feedback Through<br>Transparent Input Latch to Global Output Latch Gate          |        | 11   |      | 14.5 | _    | 18   |      | пs   |

| tigss                    | Input Latch Gate to Output Latch Setup Using Global<br>Output Latch Gate                                        |        | 16   |      | 19.5 |      | 25.5 |      | ns   |

| twigL                    | Input Latch Gate Width LOW                                                                                      |        | 7.5  |      | 7.5  |      | 10   |      | ns   |

| t <sub>PDLL</sub>        | Input, I/O, or Feedback to Output Through Transp.<br>Input and Output Latches                                   | arent  |      | 19.5 |      | 23   |      | 29   | ns   |

| tar                      | Asynchronous Reset to Registered or Latched Ou                                                                  | tput   |      | 19.5 |      | 24   |      | 30   | ns   |

| tarw                     | Asynchronous Reset Width (Note 1)                                                                               |        | 14.5 |      | 18   |      | 24   |      | ns   |

| t <sub>ARR</sub>         | Asynchronous Reset Recovery Time (Note 1)                                                                       |        | 10   | - 1  | 12   |      | 18   |      |      |

| t <sub>AP</sub>          | Asynchronous Preset to Registered or Latched Output                                                             |        |      | 19.5 |      | 24   |      | 30   | ns   |

| tapw                     | Asynchronous Preset Width (Note 1)                                                                              |        | 14.5 |      | 18   |      | 24   |      | ns   |

| t <sub>apr</sub>         | Asynchronous Preset Recovery Time (Note 1)                                                                      |        | 10   |      | 12   |      | 18   |      | ns   |

| tea                      | Input, I/O, or Feedback to Output Enable (Note 3)                                                               |        |      | 14.5 |      | 18   |      | 24   | ns   |

| t <sub>ER</sub>          | Input, I/O, or Feedback to Output Disable (Note 3)                                                              |        |      | 14.5 |      | 18   |      | 24   | ns   |

#### Notes:

1. These parameters are not 100% tested, but are evaluated at initial characterization and at any time the design is modified where frequency may be affected.

See Switching Test Circuit for test conditions. Switching waveforms illustrate true clocks only. Switching waveforms can be used to illustrate both synchronous and asynchronous clock timing. For example, tss is the ts parameter for synchronous clocks and tsh is the ts parameter for asynchronous clocks.

3. Parameters measured with 16 outputs switching.

0257526 0037306 916 🔳

#

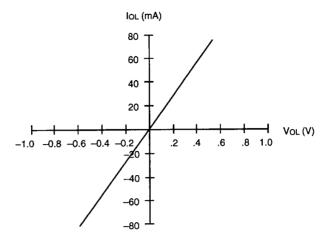

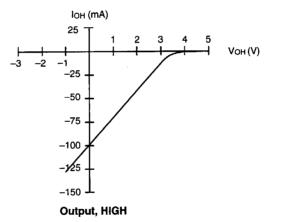

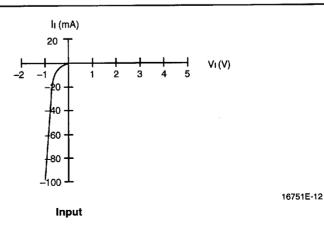

# **TYPICAL CURRENT VS. VOLTAGE (I-V) CHARACTERISTICS**

$V_{CC} = 5.0 V, T_A = 25^{\circ}C$

MACH215-12/15/20

🔳 0257526 0037307 852 💻

16751E-10

16751E-11

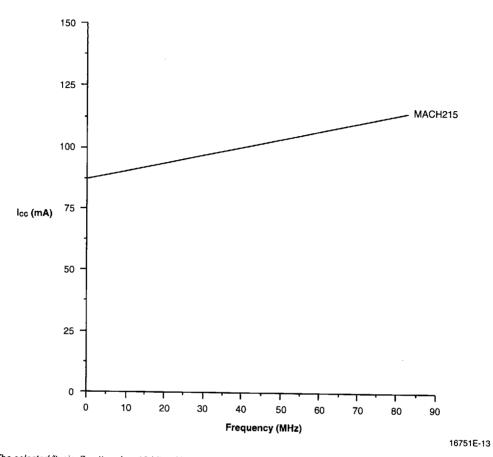

### TYPICAL Icc CHARACTERISTICS $V_{CC} = 5 V_1 T_A = 25^{\circ}C$

The selected "typical" pattern is a 16-bit up/down counter. This pattern is programmed in each PAL block and is capable of being loaded, enabled, and reset.

Maximum frequency shown uses internal feedback and a D-type register.

🛤 0257526 0037308 799 🎟

# TYPICAL THERMAL CHARACTERISTICS

Measured at 25°C ambient. These parameters are not tested.

| Parameter        |                                                         |              | Тур  |       |

|------------------|---------------------------------------------------------|--------------|------|-------|

| Symbol           | Parameter Description                                   |              | PLCC | Units |

| θјс              | Thermal impedance, junction to case                     |              | 15   | °C/W  |

| θja              | Thermal impedance, junction to ambient                  |              | 40   | °C/W  |

| <del>0</del> jma | Thermal impedance, junction to<br>ambient with air flow | 200 lfpm air | 36   | °C/W  |

| -                |                                                         | 400 lfpm air | 33   | °C/W  |

|                  |                                                         | 600 lfpm air | 31   | °C/W  |

|                  |                                                         | 800 lfpm air | 29   | °C/W  |

#### Plastic 0jc Considerations

The data listed for plastic  $\theta$  ic are for reference only and are not recommended for use in calculating junction temperatures. The heat-flow paths in plastic-encapsulated devices are complex, making the  $\theta$  ic measurement relative to a specific location on the package surface. Tests indicate this measurement reference point is directly below the die-attach area on the bottom center of the package. Furthermore,  $\theta$  ic tests on packages are performed in a constant-temperature bath, keeping the package surface at a constant temperature. Therefore, the measurements can only be used in a similar environment.

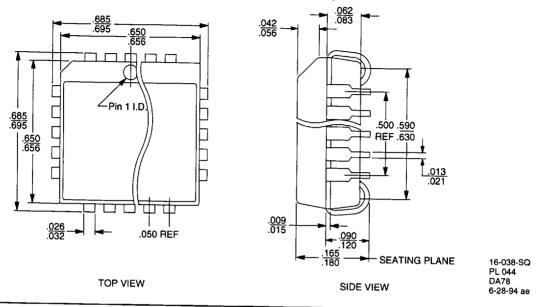

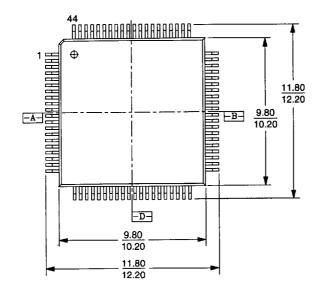

# **PHYSICAL DIMENSIONS\***

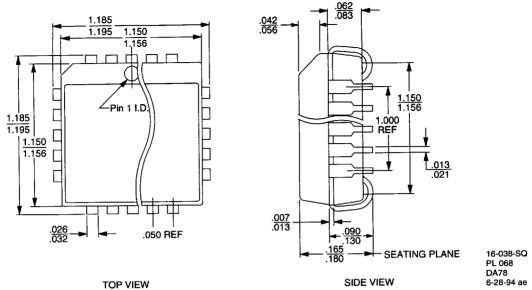

# PL 044

44-Pin Plastic Leaded Chip Carrier (measured in inches)

\*For reference only. BSC is an ANSI standard for Basic Space Centering.

\*For reference only. BSC is an ANSI standard for Basic Space Centering.

0257526 0037399 837 🎟

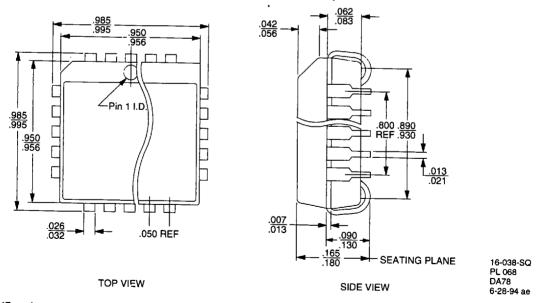

**Physical Dimensions**

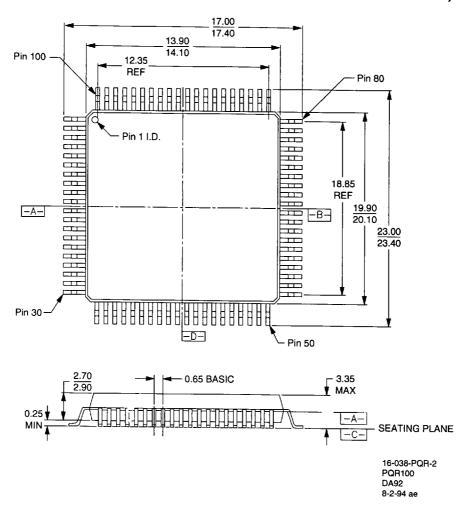

# PHYSICAL DIMENSIONS\* PQR100 100-Pin Plastic Quad Flat Pack; Trimmed and Formed (measured in millimeters)

#### Note:

Although the POR100 package is drawn as a square package, the actual package is rectangular as the dimensions suggest.

\*For reference only. BSC is an ANSI standard for Basic Space Centering.

0257526 0037400 389 🖿

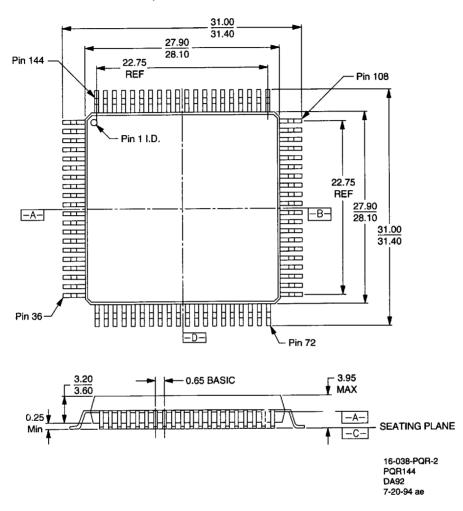

### **PHYSICAL DIMENSIONS\***

### **PQR144**

144-Pin Plastic Quad Flat Pack; Trimmed and Formed (measured in millimeters)

\*For reference only. BSC is an ANSI standard for Basic Space Centering.

3-30

**Physical Dimensions**

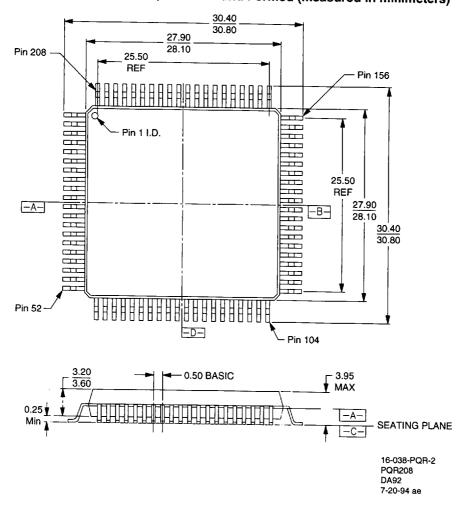

# PHYSICAL DIMENSIONS\* PQR208 208-Pin Plastic Quad Flat Pack; Trimmed and Formed (measured in millimeters)

\*For reference only. BSC is an ANSI standard for Basic Space Centering.

■ 0257526 0037402 151 |

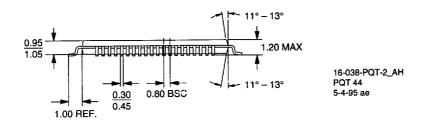

### **PHYSICAL DIMENSIONS\***

### **PQT044**

44-Pin Thin Quad Flat Pack (measured in millimeters)

\*For reference only. BSC is an ANSI standard for Basic Space Centering.

# 0257526 0037403 098 💻

**Physical Dimensions**